# LPM の利点

TECHNICAL BRIEF 24

July 1997

Altera® の FLEX® 10K デバイスのような高集積プログラマブル・ロジック・デバイス (PLD) は、設計手法に関するパラダイム・シフトを生じさせています。多くの設計者は、高集積デバイスの提供する高い性能と容量をフルに活用するため、従来の回路図をベースにした設計手法からハードウェア記述言語 (HDL) やメガファンクションそして LPM ( Library of Parameterized Modules ) などを使用した新世代の設計手法への移行を進めています。このテクニカル・ブリーフでは、FLEX 10K, FLEX 8000 および FLEX 6000 ファミリの各デバイスの設計に LPM を使用した場合の利点について解説します。

## Library of Parameterized Modules

LPM を使用する第一の目的は、シリコンの効率を犠牲にすることなく、特定のアーキテクチャに依存しないデザインを可能にすることです。LPM を使用することで、設計者はデザイン・フローの最終段階まで、ターゲットとなるデバイスのアーキテクチャを決定する必要がなくなります。この場合、デザイン入力とシミュレーションのツールはアーキテクチャに依存しないものとなり、作成したデザインを論理合成ツールまたはフィッティング・ツールにより多様なアーキテクチャに対して効率的にマッピングさせることができます。

現在、LPM には下記に示すパラメータ化された 25 種類のファンクションが含まれています。設計者は各デザインの要求に合わせて各ファンクションのサイズと特性をカスタマイズすることができます。例えば、設計者は、lpm\_mult のファンクションに提供されている LPM\_LATENCY のパラメータの値を設定することによって、パイプラインの段数を指定することができます。

- |                |                |               |

|----------------|----------------|---------------|

| ■ lpm_constant | ■ lpm_ttable   | ■ lpm_abs     |

| ■ lpm_latch    | ■ lpm_and      | ■ lpm_outpad  |

| ■ lpm_rom      | ■ lpm_shiftreg | ■ lpm_xor     |

| ■ lpm_add_sub  | ■ lpm_mux      | ■ lpm_ram_io  |

| ■ lpm_fsm      | ■ lpm_counter  | ■ lpm_compare |

| ■ lpm_inv      | ■ lpm_inpad    | ■ lpm_bustri  |

| ■ lpm_ff       | ■ lpm_or       | ■ lpm_bipad   |

| ■ lpm_decode   | ■ lpm_ram_dq   |               |

| ■ lpm_mult     | ■ lpm_clshift  |               |

## LPM のサポート

LPM はアルテラやシノプシスを含む幅広いデバイス・ベンダと EDA ツール・ベンダによってサポートされています。表 1 は LPM に対するデバイス・ベンダによるサポート状況を、表 2 は LPM をサポートしている EDA ベンダのツールを示したものです。

表 1 各デバイス・メーカーによる LPM に対するサポート状況

| ベンダ名   | LPM 委員会<br>のメンバ | LPM をサポート<br>したツール | コメント                                                |

|--------|-----------------|--------------------|-----------------------------------------------------|

| アルテラ   | ✓               | ✓                  | LPM のサポートに関する業界のリーダ。 MAX+PLUS II のすべての構成で LPM をサポート |

| ザイリンクス | ✓               |                    | LPM ではなく同社独自の XBLO™ および LogiBLO™ の手法をサポート           |

| ルーセント  |                 |                    | LPM に関する計画はなし                                       |

| アクテル   | ✓               | ✓                  | いくつかの LPM ファンクションをサポート                              |

表2 LPMをサポートしているEDAツール

| ツールの種類         | ケイデンス      | メンター・グラフィックス      | シノブシス        | ビューロジック       |

|----------------|------------|-------------------|--------------|---------------|

| ビヘイビア・シミュレータ   | Leapfrog   | QuickHDL          | 注(1)         | 注(1)          |

| 論理合成           | Synergy    | Exemplar, Galileo | FPGA Express | ViewSynthesis |

| ゲート・レベル・シミュレータ | Verilog XL | QuickSim II       | 注(1)         | ViewSim       |

| 回路図入力          | Concert    | Design Architect  | 注(1)         | ViewDraw      |

注:

(1) LPM ファンクションをサポートした製品は現在のところ供給されていません。

アルテラはLPMに対して積極的なサポートを提供しており、EIA ( Electronic Industries Association 米国電子工業会 ) のLPM委員会のメンバーであると共に、LPMをサポートしたツールも供給しています。アルテラのMAX+PLUS II 開発システムでは lpm\_fsm、lpm\_ttable、lpm\_inpad、lpm\_outpad、lpm\_bipad を除くすべての LPM ファンクションがサポートされています。

各 LPM ファンクションは FLEX アーキテクチャの利点を最大限に活用して構成され、FLEX デバイス内に最高の性能が実現されます。例えば、表3に示されているように、FLEX デバイスに実現されるマルチプライヤ ( 乗算器 ) は、他社のデバイスに実現された場合よりも高性能となります。マルチプライヤはほとんどの DSP システムにおける基本ビルディング・ブロックとなるため、マルチプライヤの性能はシステム全体の性能に大きな影響を及ぼす重要な要素となります。

表3 マルチプライヤの性能比較

| 構成                           | 性能                                      |                                         |                                         |                                       |                                         |                                       |

|------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|---------------------------------------|-----------------------------------------|---------------------------------------|

|                              | アルテラ<br>FLEX 10K(1)<br>-3 スピード・<br>グレード | アルテラ<br>FLEX 800(1)<br>-2 スピード・<br>グレード | アルテラ<br>FLEX 600(1)<br>-2 スピード・<br>グレード | ザイリンクス<br>XC4000E<br>-2 スピード・<br>グレード | ルーセント<br>OR2C15A(2)<br>-4 スピード・<br>グレード | アクテル<br>1200XL(3)<br>-1 スピード・<br>グレード |

| 8 × 8 マルチプライヤ<br>パイプライン構成    | 131                                     | 132                                     | 114                                     | 52 注(4)                               | 96                                      | 44                                    |

| 8 × 8 マルチプライヤ<br>非パイプライン構成   | 37                                      | 44                                      | 38                                      | 29 注(5)                               | 24                                      | 14                                    |

| 12 × 12 マルチプライヤ<br>パイプライン構成  | 80                                      | 81                                      | 78                                      | 38 注(4)                               | 注(6)                                    | 注(6)                                  |

| 12 × 12 マルチプライヤ<br>非パイプライン構成 | 21                                      | 22                                      | 22                                      | 21 注(5)                               | 注(6)                                    | 注(6)                                  |

| 16 × 16 マルチプライヤ<br>パイプライン構成  | 53                                      | 69                                      | 59                                      | 注(6)                                  | 55                                      | 28                                    |

| 16 × 16 マルチプライヤ<br>非パイプライン構成 | 19                                      | 21                                      | 20                                      | 18 注(5)                               | 7                                       | 8                                     |

| 32 × 32 マルチプライヤ<br>パイプライン構成  | 28                                      | -                                       | -                                       | 注(6)                                  | 注(6)                                    | 注(6)                                  |

注:

- (1) Source: Altera Applications.アルテラのマルチプライヤは、3段のパイプライン構成となっている 8 × 8 のマルチプライヤを除いて、すべて 4 段のパイプライン構成となっています。

- (2) Source: Synario App Review September 9, 1996, page-11. Lucent Microelectronics Field-Programmable Gate Array Data Book October 1996. ルーセントのマルチプライヤは 3 段、6 段、9 段と多様なパイプライン構成を使用しています。

- (3) Source: Actel Application Note Implementing Multipliers in Actel FPGAs. アクテルのマルチプライヤは 3 段のパイプライン構成となっています。

- (4) Source: Synario App Review, September 9, 1996, page-20.

- (5) Source: Synario App Review, September 9, 1996, page-20. Xilinx The Programmable Logic Data Book, September 1996. この性能値は、セットアップ・タイム、clock-to-output 延延、配線延延を加算し、この逆数から周波数を得たものです。ザイリンクスのマルチプライヤは 4 段のパイプライン構成となっています。

- (6) 現在までのところ、データが提供されていません。

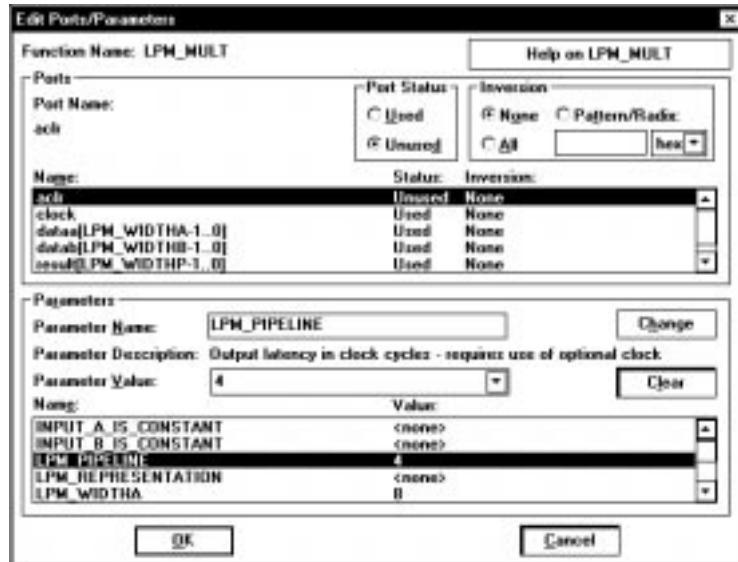

LPMとMAX+PLUS II開発システムを使用することで、任意のサイズのマルチプライヤが分単位で自動的に作成することができます。また、LPM\_LATENCYのパラメータ値を設定することによって(例:LPM\_LATENCY=2)キャリー・チェインを活用したFLEXのアーキテクチャに最適化されたパイプライン構造のマルチプライヤを作成することができます。さらに、LPMを使用することによって、各アプリケーションにスピードと効率が最適となるように、さまざまなパイプラインの長さを短時間でテストすることができるようになります。図1はMAX+PLUS IIでlpm\_multファンクションの機能、パラメータを設定するためのダイアログ・ボックスです。

図1 lpm\_multのダイアログ・ボックス

これに対して、競合各社によるLPMに対するサポートは十分なものとなっていません。例えば、ザイリンクスはLPMをサポートするのではなく、ハイ・レベルなファンクション作成とシミュレーションのためのグラフィック・インターフェース・ツールとなっている同社独自のXBLOXとLogiBLOXを使用した設計手法をサポートしているだけです。XBLOXは、符号付きのマルチプライヤをサポートしておらず、LogiBLOXはディジタル信号処理(DSP)のアプリケーションに不可欠なマルチプライヤをサポートしていません。

詳細については下記の資料を参照して下さい。カッコ内の記号はアルテラのドキュメント番号です。

■ *LPM Quick Reference Guide (A-CAT-LPM-01)*

この資料は下記のご請求下さい。

- 日本アルテラ(株) 電話: 03-3340-9480

- 販売代理店: (株)アルティマ 電話: 045-939-6113

(株)パルテック 電話: 045-477-2000

- アルテラのWorld-Wide Webサイト <http://www.altera.com>

---

## 日本アルテラ株式会社

〒163-04 東京都新宿区西新宿2-1-1

新宿三井ビル私書箱261号

TEL. 03-3340-9480 FAX. 03-3340-9487

<http://www.altera.com/japan/>

Copyright©1997 Altera Corporation. Altera MAX, MAX+PLUS, MAX+PLUS II, FLEX, FLEX 10K, FLEX 8000, FLEX 6000はAltera Corporationの米国および該当各国におけるtrademarkまたはservice markです。他のブランド、製品名は該当各社のtrademarkです。この資料に掲載されている情報、規格などは予告なく変更される場合があります。

**ALTERA®**